Kádár Ferenc hobbi weboldala:

CNC képek, videók és egyéb bigyók…

Üdvözöllek a honlapomon!

Nincs túl sok időm a honlap csinosítására, ezér olyan amilyen, de

remélem így is találsz itt valami érdekeset.

Az oldalon található kapcsolások, rajzok, ötletek

és forráskódok szabadon felhasználhatóak.

CNC:

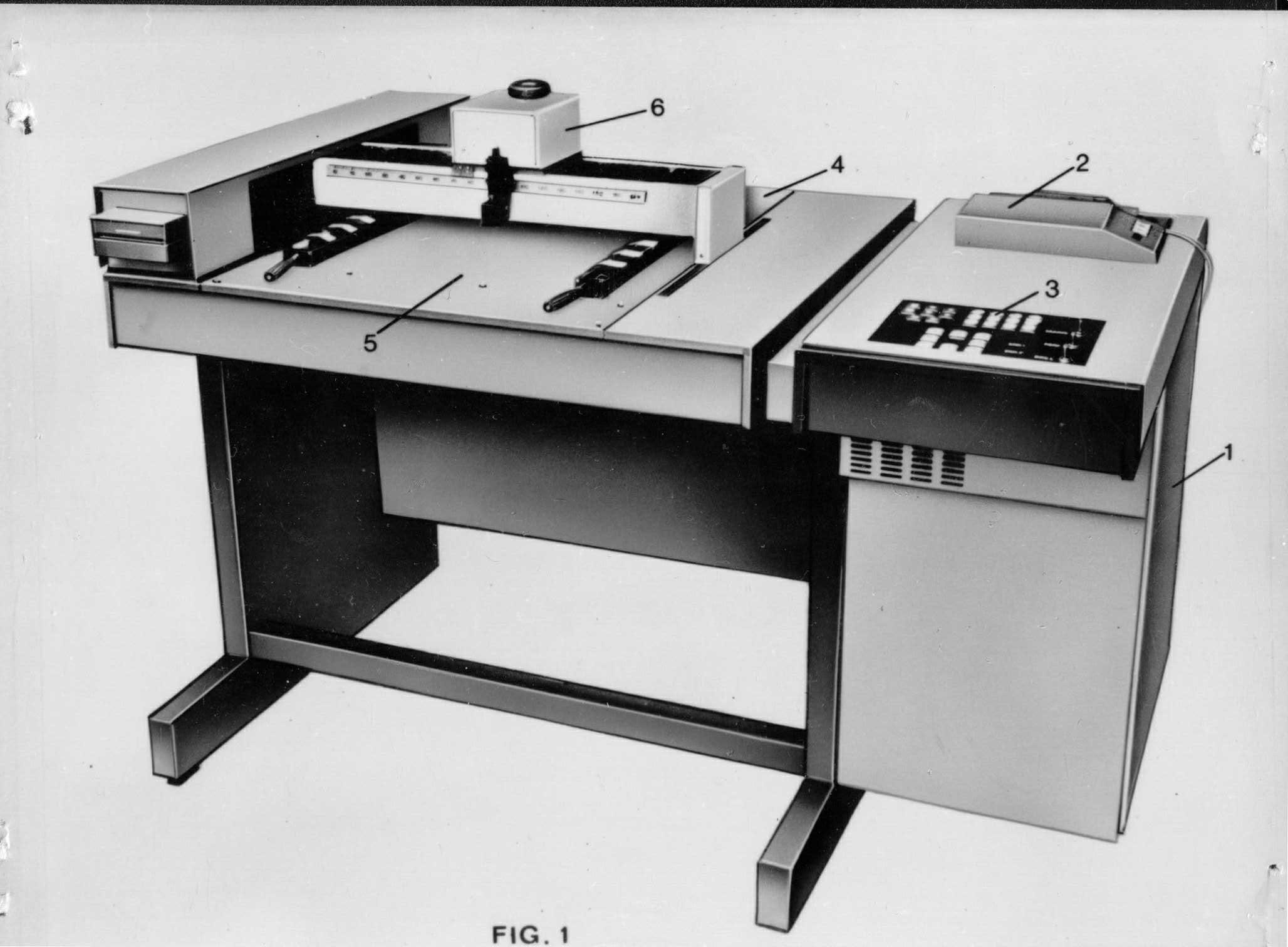

Régi FOK-GYEM gyártmányú ADMAP CNC gép átalakítása:

CPLD / FPGA :

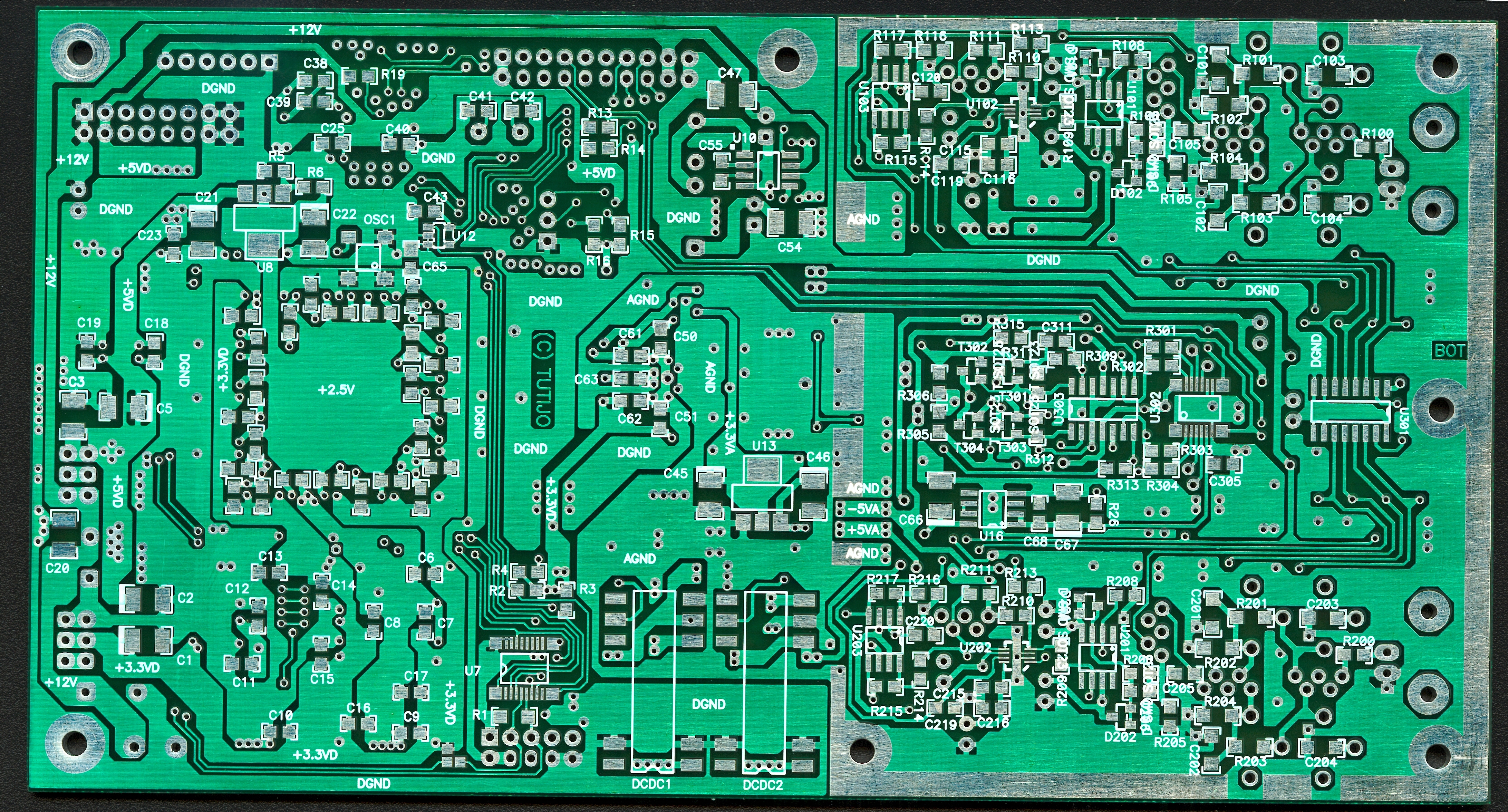

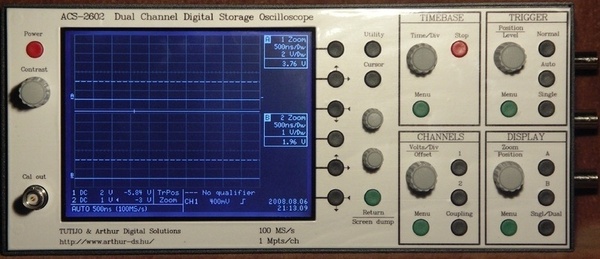

Andor barátommal közösen készített 2x100MS/s oszcilloszkóp.

Mivel nagyon profi az FPGA-s cuccok terén így a verilog kódot és

a működtető software-t Ő készítette hozzá.

A www.arthur-ds.hu oldalon lehet róla bővebben olvasni.

2 csatornás 100MS/s DSO használati utasítás: ACS2602-doku.pdf

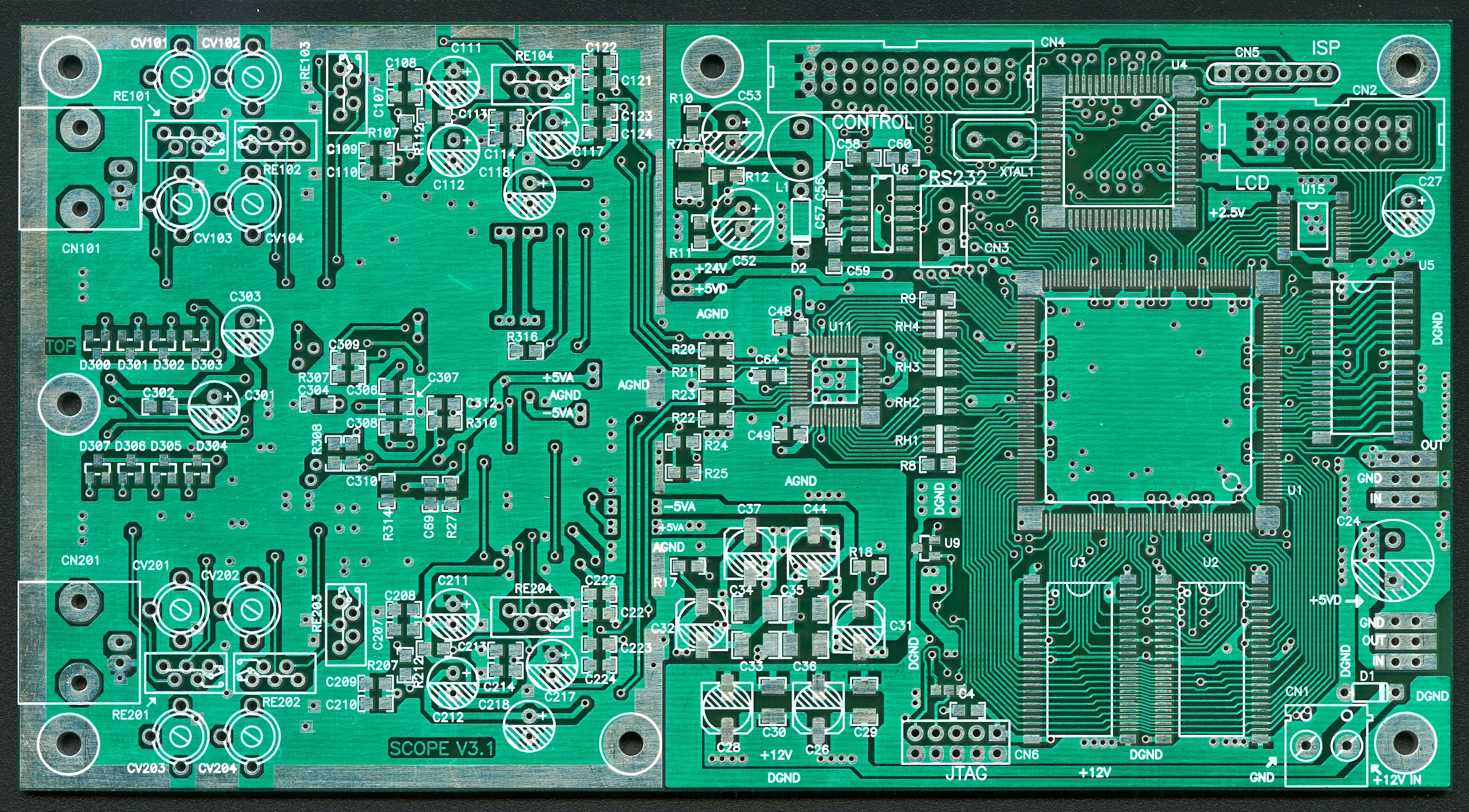

Az első komplet működő prototípushoz ezt a panel terveztem.

A következő verzió még ki lett egészítve egy EXT. trigger bemebettel

is, de arról

sajnos nincs beültetés előtti kép.

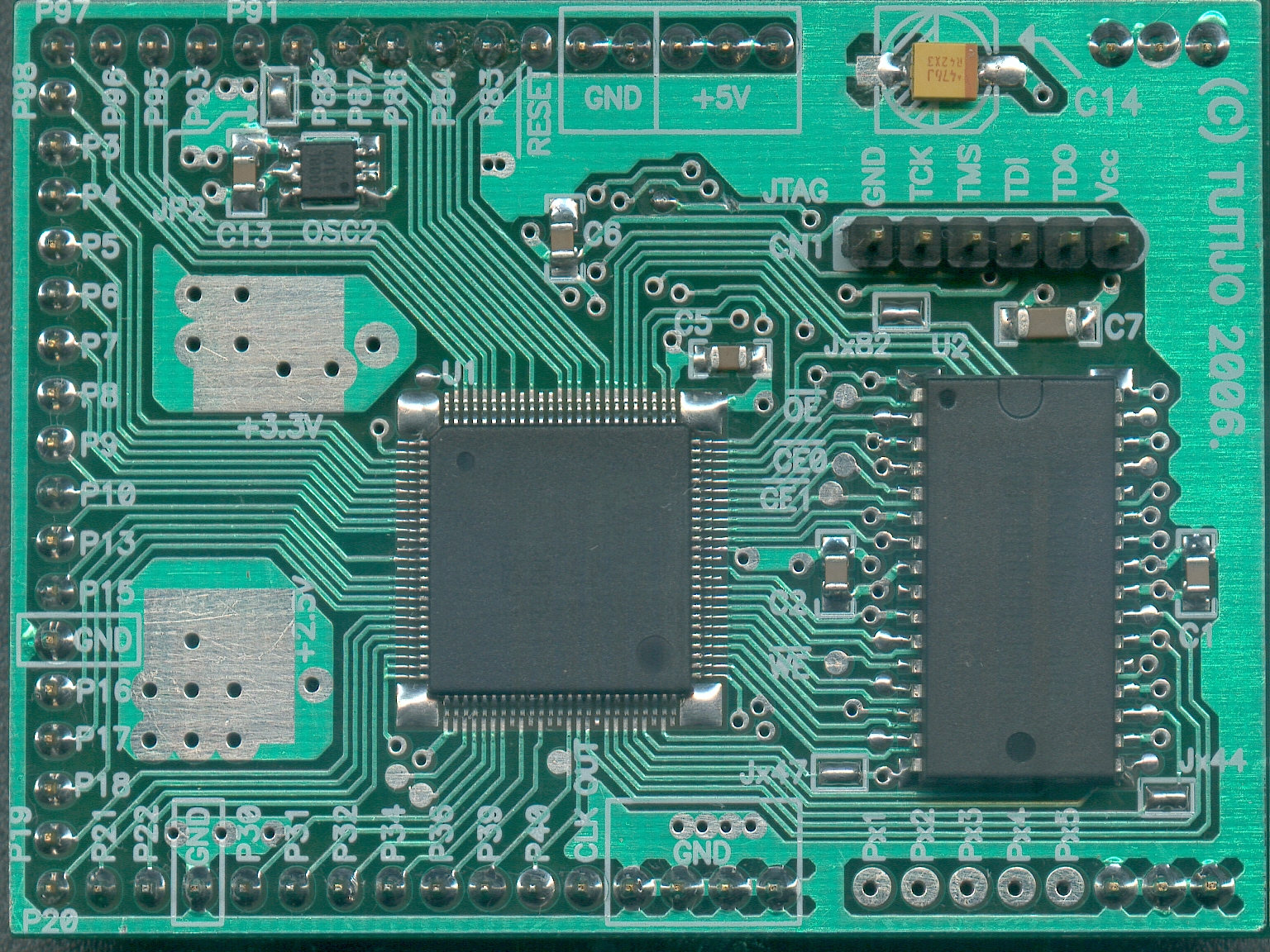

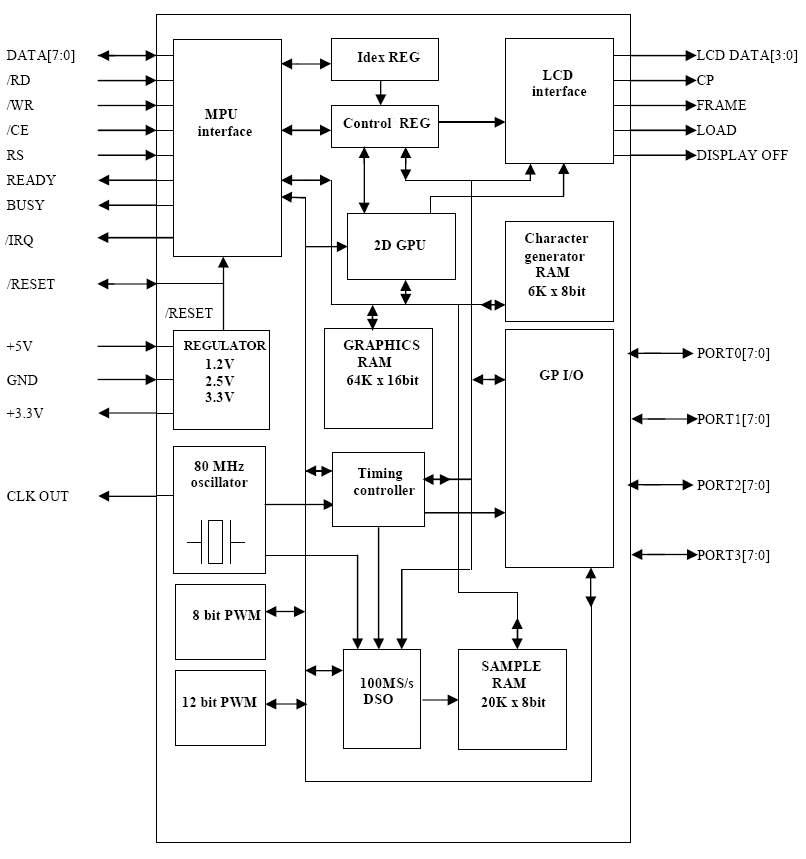

Xilinx Spartan 2-vel ( XC2S30-5VQG100C ) készített LCD kontroller

SCH, PCB, BASCOM és Verilog forráskód

Legelső kezdetleges LCD kontrollerem. 4db 2bit/pixel layer + 1 karakteres

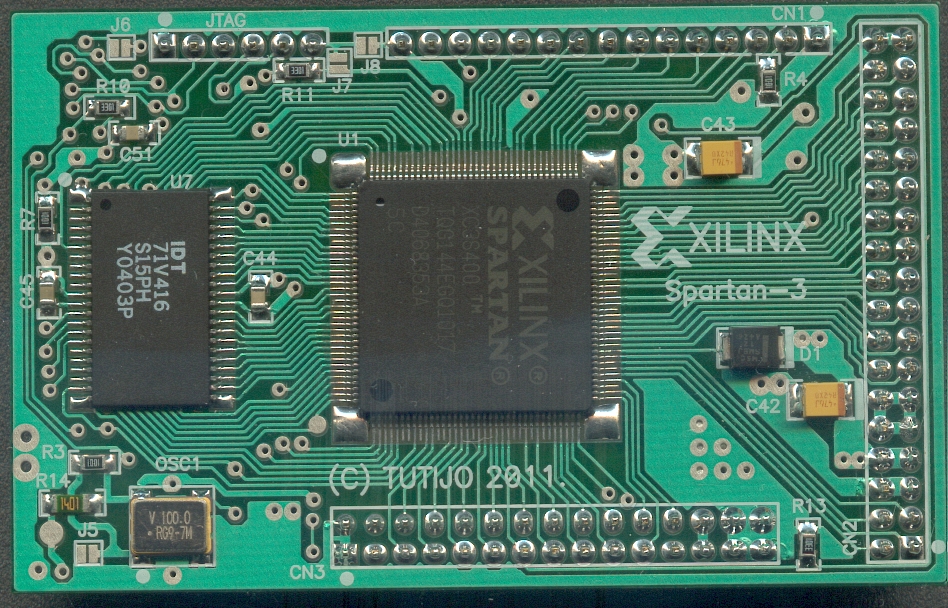

Xilinx Spartan 3 (XC3S400-5TQG144C ) LCD kontroller

Gyors 2D-s grafikus funkciókkal rendelkező mono QVGA LCD kontroller.

Mellesleg van benne egy 100MS/s DSO is. :-)

A legfontosabb tulajdonságok az alábbiak:

LCD vezérlés funkciói:

- 128 Kbyte grafikus RAM

- 320x240 felbontás

- 1bit/pixel, 2bit/pixel mód

- Külön karakteres lap

- Belső 8x8-as és 8x12-es karaktergenerátor

- egyszerre akár 512 különböző karakterhasználata

- Minden karakterhez külön tulajdonságokrendelhetőek. ( inverz, villogás, fényerő )stb.

- 3db hardware sprite 2bit/pixel -es

- Egyidejűleg a karakteres lap mellett még 4 grafikus lap és 3db sprite is megjeleníthető.

- 8 bit-es CPU interface

- 2D-s grafikus funkciók pixel,

kör, vonalrajzolás, blitter ( forgatás,tükrözés valamint pixel szintű

logikai műveletek )

- Screen capture funkció

I/O funkciók:

- 32db általánosan használható

I/O port amelyek közül több alternatív funkcióval is rendelkezik.

- Egyszerű max 100MS/s sebességű 8 bit-es DSO

1 csatorna

20 kByte RAM

Külső vagy belső trigger

Él vagy szint trigger

Állítható trigger hiszterézis

Normál vagy peak-detect

mintavételi mód

Logikai analizátor mód

- 4db inkrementális forgás jeladó kezelése

- 4db 8bit-es PWM kimenet

- 4db 12 bit-es PWM kimenet

BLOKKVÁZLAT

FPGA_Mono_QVGA_LCD_controller.pdf

Mono_LCD_Spartan3_vegleges.zip

Mono_LCD_Spartan3_vegleges_PCB.ZIP

Mono_LCD_Spartan3_vegleges_SCH.ZIP

Xilinx Spartan 3 LCD kontrollerhez scope próbapanel

Scope bemeneti fokozat és AD600 VGA-val

a próbához.

Xilinx Spartan 3 LCD kontrollerhez próbapanel

Néhány kezelőszervvel és LCD kijelzővel

kialakított próba panel a Spartan 3 chip-es modulhoz.

Spartan3_Proba_panel_kepek.zip

Spartan3_Proba_panel__BASCOM_Source_code.zip

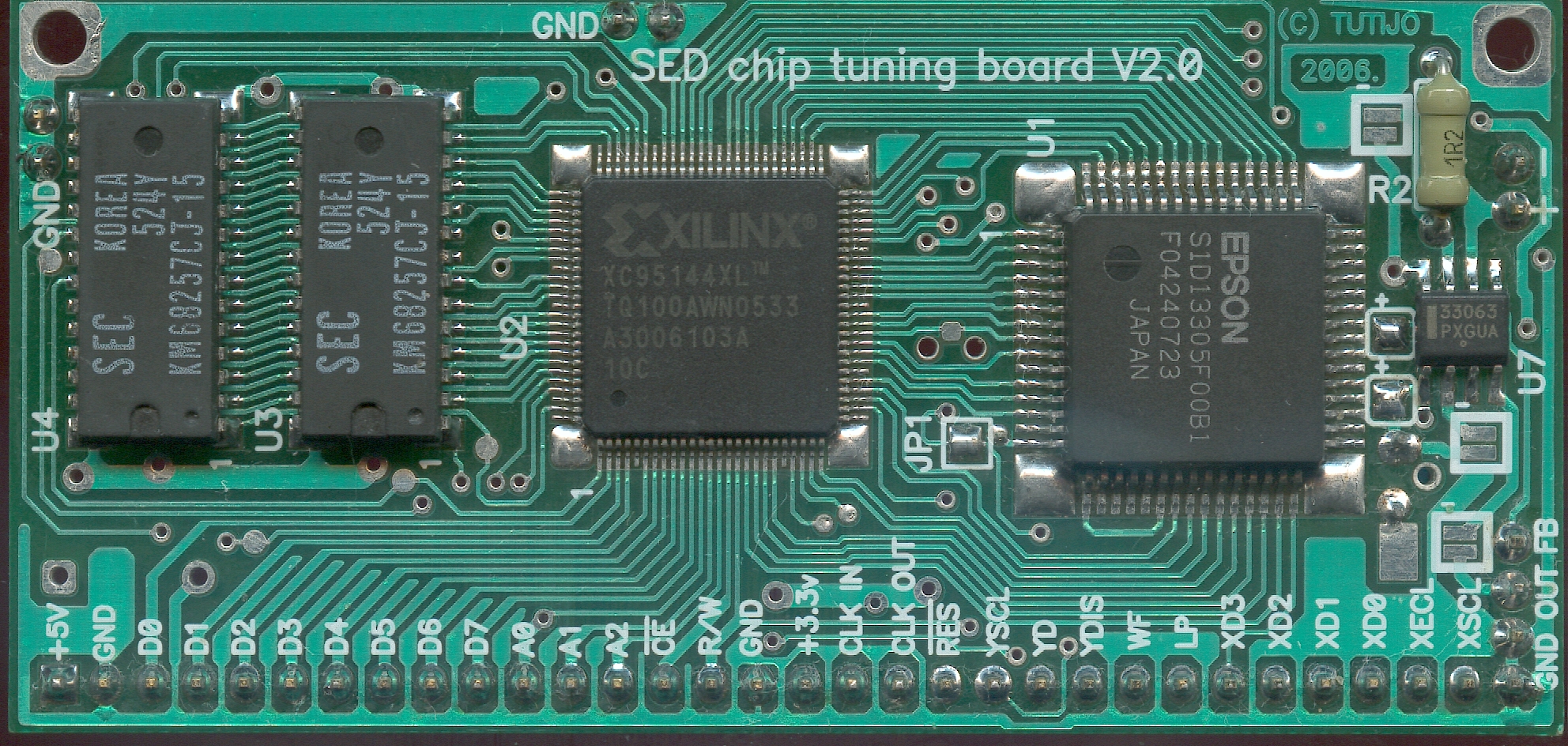

Xilinx CPLD-vel (XC95144XL-10TQG100C ) SED gyorsító panel

A SED1330 LCD kontroller idegesítő BUSY bit kezelését

teszi szükségtelenné.

Kb. 6Mbyte/sec adatátviteli sebességet biztosít és az egyik grafikus layer fél fényerővel

történő megjelenítését is lehetővé teszi.

Anno amikor készítettem, akkor még nem nagyon értettem a CPLD és az

FPGA

tervezéshez így

csak az ötlet és a hardware megvalósítását csináltam

én. A verilog kód Andor barátom munkája.